通用频率综合器芯片是一种以高精度参考源为基础,生成精确稳定输出频率的电子设备,其工作原理通常基于锁相环(PLL)或直接数字合成(DDS)等技术,通过集成压控振荡器(VCO)、鉴相器、环路滤波器等组件实现频率的合成与调节。

锁相环(PLL)是通用频率综合器的核心架构,它通过反馈控制环路锁定输出频率与参考频率的相位关系。具体过程包括:鉴相器比较参考时钟信号与分频后的输出信号之间的相位差,产生误差电压;该电压经环路滤波器平滑后驱动压控振荡器(VCO),调整其输出频率直至相位差为零,从而实现输出频率的精确控制。

直接数字合成(DDS)则采用数字信号处理技术生成频率,其核心是一个相位累加器,对频率控制字进行累加,输出的相位值通过查找表转换为数字幅度值,再经数模转换器(DAC)和低通滤波器输出模拟信号。DDS具有高频率分辨率和快速转换时间的优点,但通常需与PLL结合以提升高频性能和抑制相位噪声。

工采网代理的MS5351M是一款通用频率综合器芯片,通过I2C配置,可产生从2.5kHz至200MHz的任意时钟输出。可替代晶体、晶体振荡器、锁相环、输出缓冲器。

现代通用频率综合器芯片常采用混合架构,如DDS+PLL,其中DDS提供高分辨率的低频参考信号,PLL对其进行倍频以生成高频输出,兼顾了频率灵活性和频谱纯度。设计时需优化环路滤波器、电源去耦及PCB布局,以降低噪声和提高稳定性。

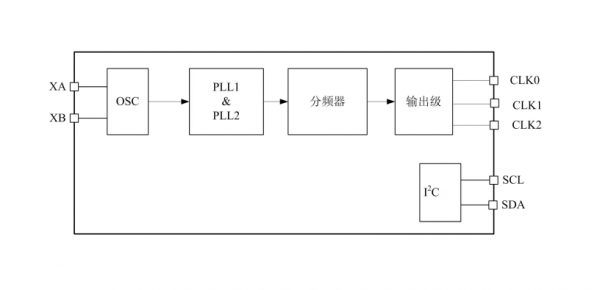

内部框图:

时钟发生芯片 - MS5351M的特性:

可3通道输出从2.5kHz至200MHz时钟

输出频率误差0ppm

高分辨率、低输出抖动

可工作在25MHz或27MHz石英晶体

输出时钟相位可调

输出延时可调

输出时钟上升/下降时间可控

频率切换无毛刺

相互独立的电源供电管脚

内部核心电路电源VDD:2.5V或3.3V

输出级电源VDDO:1.8V或2.5V或3.3V

内部高电源抑制比

兼容HCSL和PCIE Gen 1

时钟芯片 - MS5351M的应用:

高清电视,机顶盒

打印机,扫描仪,投影仪

手持设备

网络/通信

服务器

石英晶体/晶振/锁相环替代

在国产时钟发生芯片领域,瑞盟科技便是国产品牌中的佼佼者。了解更多关于瑞盟科技国产时钟发生芯片的技术应用,联系ISweek工采网“在线客服”获取产品PDF、技术支持和DEMO板、可申请样片。

转载请注明出处:传感器应用_仪表仪器应用_电子元器件产品 – 工采资讯 http://news.isweek.cn/43948.html